Daily Briefing: News Snippets

# litar EMBEDDED SYSTEMS

SUPPLEMENT

Chris A. Ciufo

Virtualization spins new architectures

**Duncan Young**

Avionics bus evolution

John Wemekamp

Heterogeneous, FPGA-based DSPs

**Guest Column**

Legacy code and security

DOM

**DiskOnModule**

# The Flash Storage Leader

### **Features**

.Ultra DMA Mode 5 Support

SLC Flash IC Technology

### Industry

- .Military Application

- .Embedded Application

- .IPC Application

- .Medical Application

- .Kiosk Application

- .Gaming Application

- .GPS/POS Application

### OS Supportings

- .DOS

- .Linux

- .Windows Vista, CE, XP

- .MAC

-40 °C degree~+85 °C degree

PQI Corporation Tel:(510)651-7281 Fax:(510)651-7240

Learn more at: www.pqimemory.com

# The MISSION WORKSTATION

for applications that demand the best.

- 4 completely independent computer systems in one 19" 6U rack mount enclosure

- Every Mission Workstation is screened to a ruggedized production acceptance test including fully powered 3G NAVMAT vibration test and environmental stress screening (ESS) test.

- Can be factory configured to be powered from DC or AC sources

- All hard drives are removable

- Temperature range of -10C to 60C

- Each of the 4 computers can be independently configured with Core 2 Dual or Core 2 Quad Intel processors

- Supports multiple operating system configurations Can be factory configured as 4 independent computer systems or one cluster computer

- Each individual computer has 2 PCI slots, 1 PCIx-16 slot, up to 8G RAM, 4 SATA ports, 2 Gigabit Ethernet ports, and up to 12 USB 2.0 ports

- Jacyl Technology is the OEM of the Mission Workstation, contact us for custom configurations

Jacyl Technology specializes in the design and production of custom and COTS electronic systems for severe environment applications.

# EMBEDDED SYSTE

July/August 2008 Volume 4 Number 5

### **COLUMNS**

### Field Intelligence

Avionics bus interface evolution

By Duncan Young

### Mil Tech Insider

New FPGAs slot into heterogeneous 10

**DSP systems** By John Wemekamp

### **Legacy Software Migration**

12 Legacy code in the security-critical age

By Bill St. Clair, LDRA Technology

### **Crosshairs Editorial**

46 Virtualization yields hardware optimization and new embedded

architectures

By Chris A. Ciufo

### **DEPARTMENTS**

39,42,43 Editor's Choice Products

**Daily Briefing: News Snippets** 14

By Sharon Schnakenburg

**New Products** 44

By Cliff Witte

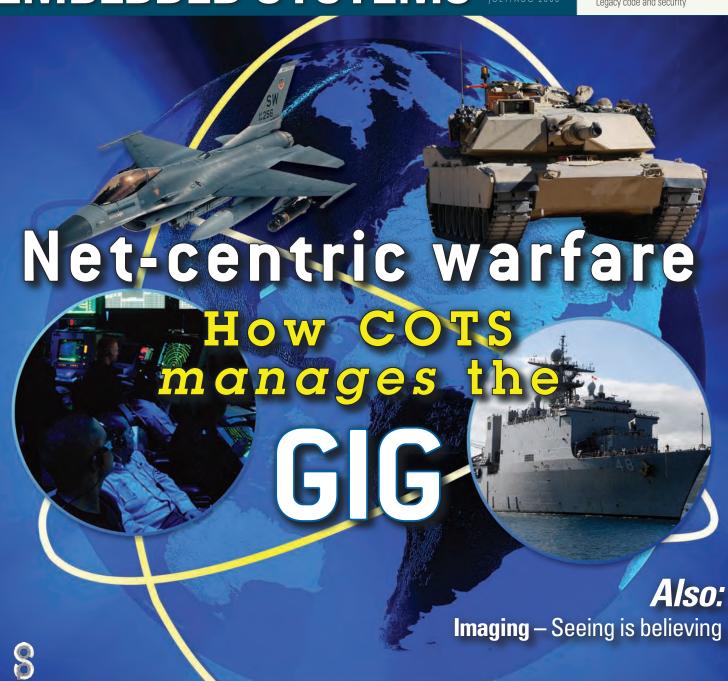

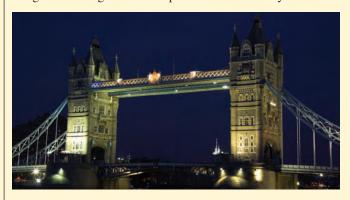

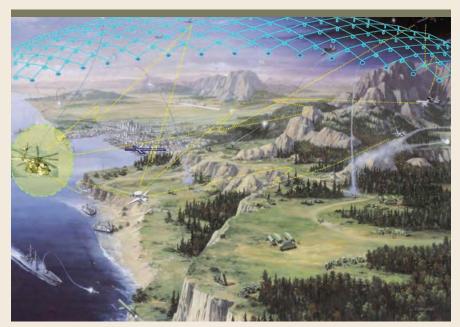

#### ON THE COVER:

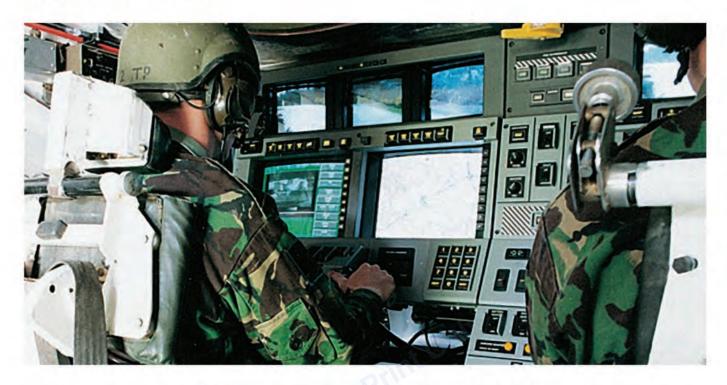

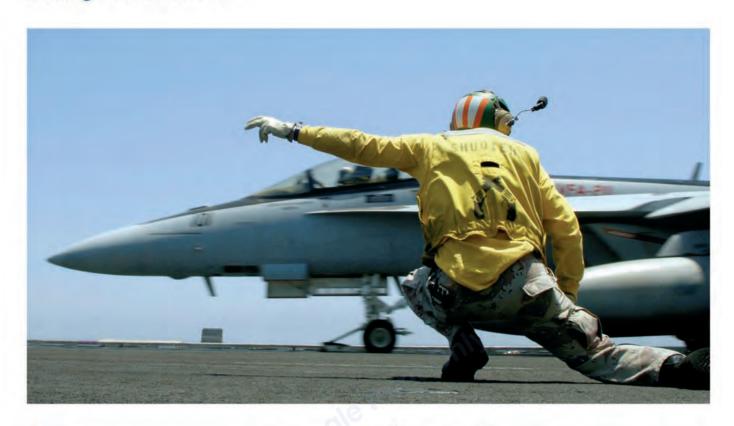

The digitized battlefield has become the Global Information Grid (GIG), where ground-, -, sea-, and space-based assets interconnect via myriad networks. But while commercial technology gives us choices for net-centric warfare, COTS also provides ways to implement, manage, and test battlefield networks. See the articles starting on page 30. (Images courtesy of DoD, U.S. Navy, and U.S.M.C.)

### **WEB RESOURCES**

Subscribe to the magazine or E-letter:

www.opensystems-publishing.com/subscriptions

### Live industry news:

www.mil-embedded.com/news www.opensystems-publishing.com/news/submit

### Submit new products:

www.opensystems-publishing.com/vendors/submissions/np

Published by:

### Technology: Imaging - Seeing is believing

Real-time image compositing: Software displaces hardware for radar displays By Dr. David G. Johnson, Cambridge Pixel Ltd.

Advanced image processing enables UAVs to fulfil their potential

By Doug Scott, GE Fanuc Intelligent Platforms

26 Remote Monitoring Debriefing System (RMDS) conceived and developed by the Israel Aircraft Industru (IAI)

By Yehuda Singer, PhD, Beyond2000 Ltd.

### Mil Tech Trends: Embedded net-centric warfare

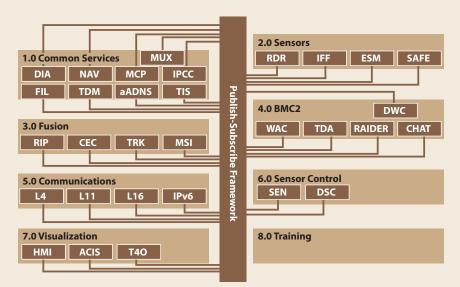

Implementing net-centric tactical warfare systems

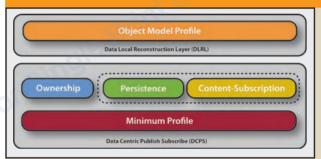

By Gordon Hunt, Real-Time Innovations, Inc.

Conquering new military network management challenges

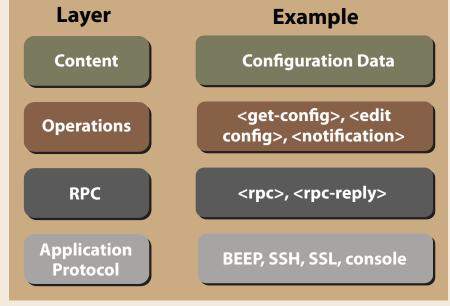

By Carl Moberg, Tail-f Systems

Denser networks, denser devices The question is: how to test the I/O ports?

By Wayne Smith, Agilent Technologies

### **E-LETTERS**

www.mil-embedded.com/eletter

Case study: LiDAR system provides helicopter pilots a clear line of sight in brownouts

By Maureen Campbell, Neptec

New consumer technology does not equal ideal COTS

By Rob Kraft, AdvancedIO Systems Inc.

Job (in)security

By Dr. Kelvin Nilsen, Aonix North America, Inc.

COTS: That which can change, changes

By Peter Cavill, GE Fanuc Intelligent Platforms

Sometimes 6U's size beats 3U: VMETRO talks about volume efficiency, FPGAs, and defense programs

Q&A with Thomas Nygaard, VMETRO, Inc.

### **EVENTS**

Intel Developer Forum (IDF)

August 19-21, 2008 Moscone Center West . San Francisco, California

www.intel.com/idf

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

© 2008 OpenSystems Publishing © 2008 Military Embedded Systems

# Real Cost Savings in MicroTCA™ Begins with Performance Technologies.

Finding the cost savings promised with MicroTCA™ may seem like trying to pull a rabbit out of a hat. And while others may discuss low cost, Performance Technologies' revolutionary, 1U highly integrated MTC5070 delivers the true promise of MicroTCA in an affordable platform. With **volume prices under \$2000**, this high-performance platform is available right now for your most demanding applications.

### Industry Firsts for a 1U MicroTCA Chassis:

- Superior Front-to-Back Cooling

- Innovative New Architecture Minimizes Cost and Profile

- Highly Integrated Infrastructure includes Ethernet Switch, PCI Express® Switch, Dual 1 GbE Uplinks, and Platform Management

- Low-cost Enterprise-class Removable Power Supply (AC or DC)

### Additional World-Class Features Include:

- 6 AMC Slots (Supports Mid or Full, Single or Double Sizes)

- · Low Profile (1U), High Density

- Plated Steel Chassis

- Completely MicroTCA.0 Compliant and Designed for NEBS

It's no longer an illusion. Call Performance Technologies today to turn your MicroTCA project into a deliverable, cost-effective reality.

For more information, download our white paper today:

MicroTCA™ Flexible, Scalable, and Cost-Effective Systems

www.pt.com/uTCA

Phone: 585.256.0200

www.pt.com/mtc5070

E-mail: info-request@pt.com

# OpenSystems Publishing

### Advertising/Business Office

30233 Jefferson Avenue St. Clair Shores, MI 48082

Tel: 586-415-6500 Fax: 586-415-4882

**Vice President Marketing & Sales**

Patrick Hopper

phopper@opensystems-publishing.com

**Business Manager**

Karen Lavman

### Sales Group

**Dennis Dovle**

Senior Account Manager

ddoyle@opensystems-publishing.com

Tom Varcie

Senior Account Manager

tvarcie@opensystems-publishing.com

**Doug Cordier**

**Account Manager**

dcordier@opensystems-publishing.com

Andrea Stabile

Advertising/Marketing Coordinator

astabile@opensystems-publishing.com

Christine Long

E-marketing Manager

clong@opensystems-publishing.com

Advortions/Ad title

### **Regional Sales Managers**

**Ernest Godsey**

Central and Mountain States

egodsey@opensystems-publishing.com

Barbara Quinlan

Midwest/Southwest

bquinlan@opensystems-publishing.com

Denis Seger

Southern California

dseger@opensystems-publishing.com

Sydele Starr

Northern California

sydele@pacbell.net

Ron Taylor

East Coast/Mid Atlantic

rtaylor@opensystems-publishing.com

### **International Sales**

Dan Aronovic

Account Manager - Israel

daronovic@opensystems-publishing.com

Account Manager - Asia

sfan@opensystems-publishing.com

### Reprints and PDFs

Nan Lamade: 800-259-0470 • mesreprints@opensystems-publishing.com

### ADVERTISER INFORMATION

| Page | Advertiser/Ad title                                                                                                                     |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| 41   | Acromag, Inc. – Simply powerful. Powerfully simple.                                                                                     |  |

| 11   | Aculab – Military commanders must always feel secure                                                                                    |  |

| 7    | Annapolis Micro Systems, Inc. – WILDSTAR 5                                                                                              |  |

| 28   | BMC Communications – ARINC and MIL-STD-1553                                                                                             |  |

| 48   | Curtiss-Wright – Tough DSP solutions                                                                                                    |  |

| 25   | DIGITAL-LOGIC AG – NEW standard for stackable PCI Express bus                                                                           |  |

| 17   | Excalibur Systems, Inc. – Winning hands                                                                                                 |  |

| 47   | GE Fanuc Intelligent Platforms, Inc. –<br>To you, it's a 16-bit digital receiver.                                                       |  |

| 3    | Jacyl Technology Inc. – Mission workstation                                                                                             |  |

| 34   | Microbus Inc. – Elcard wireless LAN modules                                                                                             |  |

| 33   | Pentek, Inc. – Introducing the one board                                                                                                |  |

| 5    | Performance Technologies – It's no illusion                                                                                             |  |

| 15   | PLDA – Why design from scratch?                                                                                                         |  |

| 43   | Phoenix International – Mission critical                                                                                                |  |

| 2    | PQI Corporation – DOM DiskOnModule                                                                                                      |  |

| 38   | Sealevel Systems, Inc. – High-speed USB solution                                                                                        |  |

| 32   | Simon Industries – Conduction-cooled heat frames                                                                                        |  |

| 21   | Super Talent Technologies – Reinventing storage                                                                                         |  |

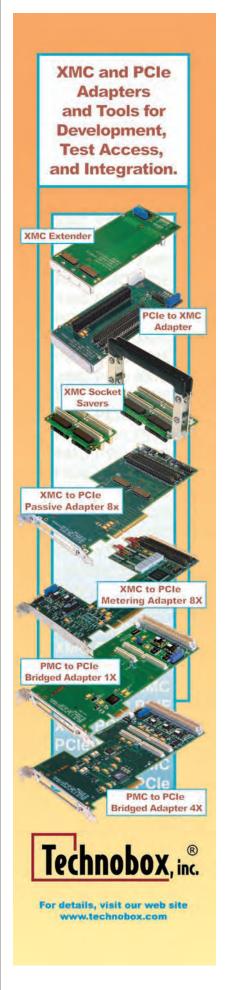

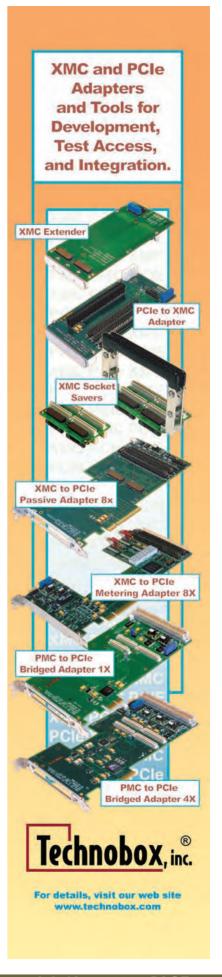

| 31   | Technobox, Inc. – XMC and PCIe adapters and tools                                                                                       |  |

| 28   | TEWS Technologies LLC – COTS I/O solutions                                                                                              |  |

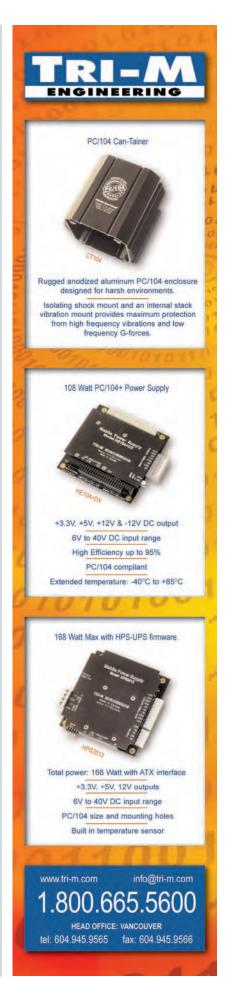

| 23   | Tri-M Systems Inc. – PC/104 solutions                                                                                                   |  |

| 19   | Tri-M Systems Inc. – TRI-M engineering                                                                                                  |  |

| 37   | Trident Space & Defense – When it absolutely, positively has to work                                                                    |  |

| 9    | VMETRO – Rugged high-speed data recording and storage                                                                                   |  |

| 13   | White Electronic Designs – Keep your design                                                                                             |  |

|      | 41<br>11<br>7<br>28<br>48<br>25<br>17<br>47<br>3<br>34<br>33<br>5<br>15<br>43<br>2<br>38<br>32<br>21<br>31<br>28<br>23<br>19<br>37<br>9 |  |

# VIIITARY EMBEDDED SYSTEMS

OPENSYSTEMS PUBLICATION

### Military and Aerospace Group

- DSP-FPGA.com Resource Guide

- DSP-FPGA.com

- DSP-FPGA.com E-letter

- Military Embedded Systems ш.

- Military Embedded Systems E-letter

- PC/104 and Small Form Factors

- PC/104 and Small Form Factors E-letter

- PC/104 and Small Form Factors Resource Guide

- VME and Critical Systems

- VME and Critical Systems E-letter

Group Editorial Director Chris A. Ciufo

cciufo@opensystems-publishing.com

Terri Thorson Senior Editor (columns)

tthorson@opensystems-publishing.com

**Associate Editor** Sharon Schnakenburg

sschnakenburg@opensystems-publishing.com

**Assistant Editor**

Robin DiPerna

**European Representative**

Hermann Strass hstrass@opensystems-publishing.com

Senior Web Developer Konrad Witte

Web Content Specialist **Creative Director**

Matt Avella Steph Sweet **David Diomede**

Art Director **Graphic Coordinator** Sandy Dionisio Circulation/Office Manager Phyllis Thompson

subscriptions@opensystems-publishing.com

## OpenSystems Publishing

Editorial/Production office:

16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

Tel: 480-967-5581 Fax: 480-837-6466 Website: www.opensystems-publishing.com

Publishers John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial Rosemary Kristoff

### Communications Group

Editorial Director Joe Pavlat **Assistant Managing Editor** Senior Editor (columns) **Technology Editor European Representative**

Anne Fisher Terri Thorson Curt Schwaderer Hermann Strass

Senior Designer Joann Toth

### **Embedded and Test & Analysis Group**

**Editorial Director Editorial Director** Senior Associate Editor **Special Projects Editor European Representative**

Jerry Gipper Don Dingee Jennifer Hesse **Bob Stasonis** Hermann Strass

ISSN: Print 1557-3222

Military Embedded Systems (USPS 019-288) is published eight times a year (January/February, March/April, May, June, July/August, September, October, November/December) by OpenSystems Publishing LLC, 30233 Jefferson Avenue, St. Clair Shores, MI 48082

Subscriptions are free to persons interested in the design or promotion of Military Embedded Systems. For others inside the US and Canada, subscriptions are \$28/year. For 1st class delivery outside the US and Canada, subscriptions are \$50/ year (advance payment in US funds required).

Canada: Publication agreement number 40048627 Return address WDS, Station A PO Box 54, Windsor, ON N9A 615

POSTMASTER: Send address changes to *Military Embedded Systems* 16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

18

Winchester Electronics - Power connector solutions

# Annapolis Micro Systems The FPGA Systems Performance Leader

# WILDSTAR 5 for IBM Blade The Perfect Blend of Processors and FPGAs

Fully Integrated into IBM Blade Management System

Abundant Power and Cooling Ensure Maximum Performance

Made in the USA

## **Ultimate Modularity**

From 2 to 8 Virtex 5 FPGA/Memory Modules Input / Output Modules Include: Quad 130 MSps thru Quad 500 MSps A/D 1.5 GSps thru 2.2 GSps, Quad 600 MSps A/D Dual 1.5 GSps thru 4.0 GSps D/A Infiniband, 10 G Ethernet, FC4, SFPDP

Direct Seamless Connections with no Data Reduction

Between External Sensors and FPGAs

Between FPGAs and Processors over IB or 10GE Backplane

Between FPGAs and Standard Output Modules

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

## Field Intelligence

## **Avionics bus interface** evolution

Avionics buses are traditionally slow to evolve, partly because requirements change so slowly and partly because of the costs of development, certification, and sustainment. It is with the development of new airplanes that the demand for new bus architectures evolves. This can be seen in the adoption of Fibre Channel for JSF and ARINC 664, also known as AFDX for new Boeing and Airbus airplane types. Some buses, although ideally suited technically such as Time Triggered Protocol (TTP), have been sluggish to be adopted and might only find use in niche applications. However, although the rate of change might be slow, the nature of the market still leaves room for much innovation in packaging, soft cores, and test equipment by embedded computing vendors.

Avionics architectures typically separate the flight safety-critical elements such as primary flight control, cockpit, landing gear, and so on from less critical elements such as cabin environment, entertainment, and, in the case of military aircraft, the mission systems. This separation offers less onerous initial certification and allows incremental addition, as is often required for regulatory reasons, without the need for complete recertification. Significant savings in weight and power could be made with an integrated systems approach, using centralized computing supporting individual applications running in secure partitions with critical and non-critical data sharing the same bus. The most widely adopted of these is ARINC 664.

Other safety-critical bus technologies provide the same capability. For example, TTP is designed to provide time domain separation of groups of participants (such as nodes) on a bus. TTP can support a single fixed group or multiple groups; each participant within each group and each group are allowed time slots on the bus that are scheduled to ensure that every participant always has time to complete its data transfers. TTP can also detect whether scheduled participants are present and working correctly; it can detect transmission errors and tolerates faulty nodes. MIL-STD-1553B is similarly deterministic in its scheduling of bus traffic, but TTP is much more flexible and capable. However, MIL-STD-1553B is firmly entrenched in military avionics and mission systems. Because of this widespread use, it still remains the medium of choice for many upgrade and improvement programs.

#### Embedding MIL-STD-1553B

Typical COTS-based military avionics subsystems use modules such as VMEbus, CompactPCI, or VPX configured in an enclosure. It is a key requirement to add MIL-STD-1553B interfaces in a modular form to these subsystems, and the PMC form factor is the preferred choice. Other solutions include small mezzanines on SBCs or entire dedicated modules, adding eight or more dualredundant interfaces into a single subsystem. But small-scale

embedded subsystems can now be implemented as a System-on-Chip (SoC) using the latest generations of FPGAs. This creates opportunities for COTS vendors to offer 1553 IP cores for single or multiple remote terminals, bus controller, and bus monitor functions, extending the COTS value proposition well beyond the traditional board supplier.

### Avionics interfaces on ExpressCard

With the continued development of new applications for avionics interfaces, bus analyzers play an important role in the testing and verification process. Similar to many market sectors, the laptop computer has become the ubiquitous test vehicle, easily supporting the four basic analyzer functions of display, logging and analysis, simulation, and playback when hooked up to a test rig or aircraft system. The laptop's PCMCIA slot has, until recently, been used to connect to the system under test. However, PCMCIA is rapidly being displaced by the new ExpressCard standard. This replaces the parallel interface of PCMCIA with PCI Express, offering significant improvements in performance and bandwidth plus compatibility with many other forms of embedded computing technology.

Despite its small size, an ExpressCard can support a dualredundant AFDX port, logging all bus traffic, complete with 64-bit time tagging and IRIG-B for synchronization with external time sources. The RAF-EC AFDX ExpressCard module (Figure 1) is designed for use in avionics bus analyzers, along with its sibling ExpressCard products for MIL-STD-1553B and ARINC 429. The RAF-EC and MIL-STD-1553B

While it appears that avionics buses are being left behind by the pace of technological change, there are sound economic and safety reasons why avionics architectures cannot change so rapidly.

soft cores are produced by GE Fanuc

Appropriate new technologies such as TTP, developed for the automotive sector, are slow to migrate from their native markets even with proven certification to RTCA requirements. However, the pace of technological change will ensure that competitive innovation will continue to refine and improve the choices of avionics bus products available from the COTS market.

To learn more, e-mail Duncan Young at young.duncan1@btinternet.com.

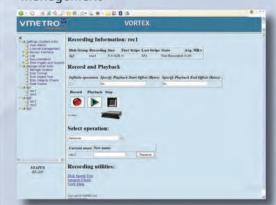

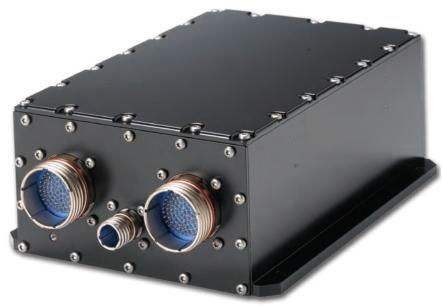

# Rugged High-Speed Data Recording and Storage

Vortex Data Recording and Playback Systems

Fibre Channel Storage Area Network

Solid State or Rotating Media

### Powerful

- Streaming data recording platforms with up to 720 MB/s per recording engine sustained recording performance

- Scalable Fibre Channel SAN architecture providing virtually limitless storage capacity

- Ready-to-run application examples

### **Flexible**

- Customer programmable or application specific recording and playback systems

- VXS (VITA 41), VME, CompactPCI and Industrial PC recording engines

- Solid state or rotating media options from rugged to commercial

### Innovative

- Access and control using web browser or XML-RPC

- Disk grouping and intelligent disk management

Embedded Computing - Data Recording/Rugged Storage - Bus/Protocol Analyzers

For more information, please visit http://www.vmetro.com/recorder or call (281) 584-0728

# Mil Tech Insider

# New FPGAs slot into heterogeneous DSP systems

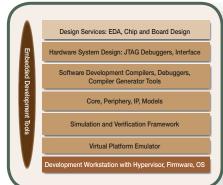

By John Wemekamp

There is no doubt that FPGAs with their large arrays of multipliers have transformed the repetitive, parallel processing of sensor data at the front end of DSP systems such as radar, signals intelligence, and Electro-Optical/Infrared (EO/IR). Although earlier FPGAs offered the computational performance required, integrating the FPGA with the next level of processing while achieving optimal performance and dataflows required specialized skills as well as intimate application knowledge. The latest generation of FPGAs incorporates a much greater complement of high-speed serial I/O and embedded hard cores and/or vendor-supplied standard interface blocks such as PCI Express and Serial RapidIO. This makes them ideal for use within heterogeneous (mixed FPGA and processor) multicomputing systems. For maximum usability, this extra functionality must be supported by IP libraries and communications middleware to provide a flexible, high-performance dataflow architecture without the integration headaches.

Most military embedded computing applications have severe space, weight, and power constraints motivating designers to consider innovative remedies using the remarkable functionality of today's FPGA devices to achieve true System-on-Chip (SoC) solutions. However, complex sensor processing applications with many hundreds of channels and high data rates are unlikely to be resolved by FPGAs alone. While they are ideally suited to repetitive fixed-point algorithms such as convolution, filtering, and decimation, the resultant data streams will often need to be distributed to a further level of processing. In a large system, this would be an array of multicore Power Architecture processors with AltiVec vector processing enhancements. Such a mixed architecture is also better at supporting complex but variable processing solutions typically found in multimode radars, where an FPGA's reconfigurability can be exploited to optimize a radar's performance in different modes of operation.

### Serial connectivity

In common with other embedded sectors, there has been a rapid migration of standards-based connectivity from parallel standards such as PCI and PCI-X to the serial connectivity of PCI Express, Serial RapidIO, and Ethernet. In the military embedded market, this has been facilitated by the introduction of the VPX (VITA 46) standard and the widespread use of Freescale Semiconductor's 8641D dual core Power Architecture processor, creating a new fabric-based framework for the implementation of complex multicompute node solutions. Through advances in process technology, the latest FPGA devices – such as Xilinx's Virtex-5 or Altera's Stratix IV – incorporate many more multipliers and logic elements. They also include a significant step forward in multi GHz, high-speed I/O signaling to satisfy the new serial fabric and networked vision of system connectivity. For example, the Virtex-5 includes up to four scalable PCI Express endpoints, configurable from x1 to x8 lanes, and Serial RapidIO soft cores, as well as up to eight 10/100/1000 Mbps Ethernet Media Access Controllers (MACs).

Military DSP solutions require advanced Direct Memory Access (DMA) controllers and banks of external memory (SRAM and DDR2 DRAM) to support the buffer sizes, dataflows, and fabric ports needed to process incoming streams of data produced by Synthetic Aperture Radar (SAR) or electronics intelligence gathering equipment. In the case of the multimode radar mentioned earlier, these dataflows may vary between modes in their bandwidth and routing, highlighting the need for the flexibility offered using a switched fabric compared to fixed, point-to-point links. But the key to making use of all this additional capability lies in a common interprocessor communications layer between all processing nodes within a system, whether FPGA or Power Architecture, and a set of IP cores and tools to ease their integration.

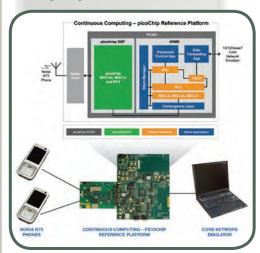

Together with the serial standards connectivity framework, these tools and IP make it possible to implement more efficient DSP solutions with mixed processing technologies, focusing on algorithm development, distribution of tasks, and dataflow rather than the time-consuming integration of disparate technologies. These principles are illustrated by the CHAMP-FX2 from Curtiss-Wright Controls Embedded Computing (CWCEC) shown in Figure 1. The VPX-compatible CHAMP-FX2 incorporates two Virtex-5 devices and a dual core 8641D processor, supported by Continuum FXtools. It includes IP in support of Serial RapidIO DMA engines, external memory controllers, and a scalable switching interconnect. All these are optimized for operation over rugged temperature ranges.

Figure 1

Today, many more mixed sensor/generalpurpose processing applications are turning to FPGAs for an affordable, practical solution. Practical heterogeneous computing architectures will be the way to resolve the diminishing space, weight, and power versus performance dilemma. FPGA devices properly supported by COTS vendors' IP and tools, such as the Virtex-5 or Stratix IV, have the logical, arithmetic, and I/O capability to perform front-end DSP operations. In addition, they can slot into heterogeneous, serialstandards based computing systems, satisfying the military's complex future multicomputing applications.

To learn more, e-mail John at john.wemekamp@curtisswright.com.

# Military commanders must always feel secure with their communications systems... DO YOU?

## Our expertise

Aculab has become a center of excellence for many agencies delivering network centric communications solutions for deployment in tactical and infrastructure networks throughout the defense technology sector. Our advanced enabling technologies and responsive commitment to bespoke engineering development provide essential interoperability and highly effective, redundant, reliable and scalable components that enable our partners to deliver secure applications for joint land, sea and air operations.

### Our difference

When you invest in a partnership with Aculab, you get more than the highest quality media processing technology that has been optimized for your sector. Whether it's for military applications, contact centers, conferencing or fax technologies, you get the reassurance of a stable and proactive partner, offering continued support and enabling you to adapt to change before it happens.

### Our technology brings you

- Reduced operating costs

- Faster time to market

- Improved margins and ROI

# For further information

www.aculab.com/military info@aculab.com +1 781 433 6000

+44 (0) 1908 273802

The cost and convenience advantages of legacy code reuse can be diminished or complicated when security and safety-critical risks are considered. If the legacy code is proven to be functionally correct and operationally viable, its acceptance is based on an assumption of what is expected to happen. However, it is the unexpected that typically causes faults, and structural testing provides a means of mitigating the unexpected.

Today, the "as built" acceptance of legacy software is coming under more scrutiny. This is due, in both military and commercial systems, to an increasing emphasis on security and safety evaluation criteria. With respect to software aspects of certification, there is a mandatory requirement for evidence of a repeatable verification process and the analysis that supports it. Structural testing is a mechanism to validate this evidence.

Although once viewed as an unnecessary cost burden, a rigorous, standards-based development and verification process comes as a consequence of the emerging global perspective on the importance of safety in embedded systems industries worldwide. This perspective is defined by risks associated with activities as diverse as commercial air travel, medical equipment product deployments, global automotive product development standardization, and defense and security. In these applications, the liabilities, costs, and mission impacts associated with unexpected software and system behaviors are considered unacceptable.

As a member of the FAA's international working group on flight software, which is producing the next version of its DO-178 software standard, I have witnessed the growing awareness of the use of legacy software in flight software systems. The working group has strived to ensure that legacy code is properly managed, verified, and that it does not in fact become "dead" or inaccessible code where it could inadvertently be invoked for runtime execution without having been previously and properly tested. Historically, dead code has been seen as a cause of unexpected software behavior and poses a significant risk to flight safety.

With the emergence of object-oriented applications in embedded systems, using languages such as C++, Java, and Ada 2005, the working group has also realized that the possibilities for reuse of legacy code have grown exponentially. Legacy components can share member functions with new components, and the precise behaviors of these shared functions are not actually visible before runtime execution. In object-oriented systems, the unexpected has a higher probability of occurring.

The U.S. military also recognizes the risks associated with unexpected software behaviors, especially in the context of security vulnerabilities. The Air Force Research Laboratory, in cooperation with the National Security Agency, Department of Defense prime contractors, academia, and software suppliers, is managing a Multiple Independent Levels of Security/Safety (MILS)

program to combine DO-178B with standards for security. This includes the Common Criteria and Director of Central Intelligence Directive 6/3, Protecting Sensitive Compartmented Information Within Information Systems. Though the MILS program does not directly address legacy code, many of its objectives are being applied to new projects and deployments that incorporate legacy software. The software development and verification guidance for the MILS program, which comes largely from DO-178B, now presents software suppliers and system integrators with the enormous challenge of implementing repeatable verification processes and mitigating the risks associated with unexpected software behaviors.

Given the challenges associated with security and safety-critical software, we need to identify best practices with respect to legacy code and propose a way to maintain and update legacy code. Such challenges are met through *structural testing*. Structural testing, sometimes described as "software testing software," provides a runtime environment in which test cases are auto-generated to exercise software behaviors based on a system-wide, path-level analysis of the code. Although in the past structural testing was criticized for not explicitly verifying functional correctness, this opinion fails to recognize that the goal of structural testing is to exercise the entirety of software structures, trap exceptions, and measure the resulting code coverage -not to explicitly test software functionality.

Unless the "as-built" architecture of legacy software is correctly analyzed, the impact of changes cannot be predicted nor can changes effectively be applied. Fortunately, the static analysis inherent to structural testing can also produce graphical representations of the architecture including call tree graphs, control flow graphs, data coupling tables, and set/used tables. These visualizations are especially helpful to engineers working with code from multiple origins such as modeling tools, hand code, and software libraries. Another byproduct of the static analysis dimension of structural testing is the automated application of coding rules to the source code, assuring implementation consistency between legacy and new code.

Advances in test technology have spawned a new generation of tools, not just another breed. These advances have arrived just in time to meet the needs of international software standardization, the globalization of embedded software markets, and the rising emphasis of security and safety-critical verification criteria. Now legacy software users can squeeze out unexpected software behaviors and help keep us safe and secure.

Bill St. Clair is technical evangelist for LDRA Technology in San Bruno, California and has more than 25 years in embedded software development and management. He holds a U.S. patent for a portable storage system and is inventor of a patent-pending embedded requirements verification system.

WHITE ELECTRONIC DESIGNS

www.whiteedc.com

Customer First. Quality Always.

# Daily Briefing: News Snippets

By Sharon Schnakenburg, Associate Editor

www.mil-embedded.com/dailybriefing

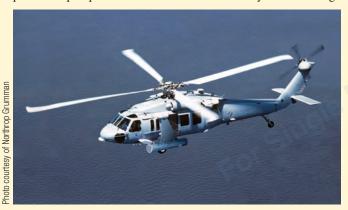

### Northrop Grumman and **U.S. Navy want more**

Northrop Grumman recently decided that enough wasn't enough, then granted a second (low-rate) initial production Central Electronics Chassis (CEC) contract to VMETRO, Inc. The contract stipulates that VMETRO provides three more CECs for the U.S. Navy's Airborne Laser Mine Detection System (ALMDS). CEC is a liquid-cooled ATR system, containing VMETRO's VPF1 quad processor payload cards and VITA 41 CSW1 switch cards. Meanwhile, the helicopter-deployed ALMDS program aids the U.S. Navy in spotting sea mines close to or at the surface of water by utilizing a blue-green laser and airborne light detection. Fiftyplus helicopter platforms are slated for ALMDS system outfitting.

### MicroTCA: Tough enough?

The debate of whether MicroTCA is really rugged enough – and for which apps – might be an open and closed case, according to Hybricon and Emerson Network Power. The closed case: Soon PICMG's MicroTCA.1 effort, which focuses on rugged industrial and commercial apps' shock, vibration, and extended temperature considerations, comes to completion. The open case: Work begins on the new PICMG Rugged MicroTCA.2 subcommittee, where Hybricon's Michael Palis serves as chair and Bob Sullivan takes on the secretary role, while Emerson's Stuart Jamieson is draft editor. Rugged MicroTCA.2 aims to address vibration and shock according to ANSI/VITA 47 for conduction- and air-cooled apps. The group will also focus on higher levels of harsh environment stressors than those covered by Rugged MicroTCA.1.

### Static analysis is improving, report reveals

With backing from the U.S. Department of Homeland Security and as part of the government's Open Source Hardening Project, Coverity recently released its Scan Report on Open Source Software 2008. The report analyzes 55 million+ code lines from more than 250 open source projects utilizing the Coverity Prevent static analysis tool over a two-year timeframe. Projects analyzed include those implementing the Linux OS and Apache Web server, among others. Findings, related to the report's Scan site, indicated: There was a 16 percent drop in static analysis defect density; false positives detected by open source developers are less than 14 percent; and projects that have a large average function length are not more likely to have higher defect densities, among other findings. The free report can be downloaded at www.coverity.com.

### **Reducing SCA conformity risks**

At the recent International Software Radio-Defence Conference held in London, Zeligsoft may have disproved the dangers of conformity. Case in point: Zeligsoft's new Code Generator v. 2.0 provides SCA device code generation, abstracting the physical radio hardware in compliance with SCA. This automated code production ensures that the platform continues to conform to the SCA specification during the full development cycle. Additionally, the company announced its SCA Core Framework (CF), an out-ofthe-box solution comprising omniORB CORBA object request broker pre-integrated with the Zeligsoft CE system-centric development environment. Zeligsoft CE is geared toward software design for heterogeneous multiprocessor/multicore systems.

### **Lockheed Martin radar completes CDR**

Getting critical isn't always a bad thing, particularly for military apps. A prime example is Lockheed Martin's (LM's) Enhanced AN/TPQ-36 counterfire target acquisition (EQ-36) radar, which has successfully completed its Critical Design Review (CDR). Consequently, the program's five radar systems are now set to start the initial production phase, with the first two systems slated for delivery to the U.S. Army by summer 2009, the third and fourth by fall 2009, and the fifth by early 2010. EQ-36 is touted to classify, detect, track, and determine locations of indirect enemy fire including artillery, rockets, and mortars in 360- or 90-degree modes. The EQ-36 will also replace outdated TPQ-36 and TPQ-37 medium-range radar, which offer only "limited" 90-degree operation. Total acquisition value could surpass \$1.6 billion, LM reports.

### SS/L sews up satellite modifications

Loral Space & Communications' subsidiary Space Systems/ Loral (SS/L) recently delivered its tailored ProtoStar I satellite to Kourou, French Guiana. The satellite - spawned from an existing satellite purchased by ProtoStar - was altered to meet defined footprint/coverage and power requirements and deployed within 17 months of contract signing. ProtoStar I, operating on C-Band and Ku-Band, will offer two-way broadband Internet services to well-established and nascent Direct-To-Home (DTH) Asian market operators. The satellite is developed around SS/L's highrel 1300 spacecraft bus and is anticipated to deliver 15+ service years. ProtoStar I, slated for launch onboard the Ariane 5 launch vehicle, is the first of several satellites on ProtoStar's docket.

Photo courtesy of Loral Space & Communications, Inc.

### It's not a world record ... or is it?

If the National Aeronautic Association (NAA) didn't see it, did it really happen? Boeing says so and has submitted their application to claim a world record to the NAA - the United States' sanctioning entity for the Fédération Aéronatique Internationale (FAI) for a recent UAV flight. The A160T Hummingbird unmanned rotorcraft executed its 18.7-hour flight on May 14-15, thereby setting a world endurance record for its class (1,102 to 5,511 lbs or 500 to 2,500 kg), Boeing claims. "We didn't set out to establish a world record, but it was a great accomplishment," states

Jim Martin, Boeing Advanced Systems A160T program manager. The flight occurred in southwestern Arizona at the U.S. Army's Yuma Proving Ground, where the aircraft transported an internal payload of 300 lbs at altitudes to 15,000 feet.

Photo courtesy of Boeing

### **Curtiss-Wright scores FCS** contract win

Forming one piece of an integrated puzzle, an \$8 million contract was recently awarded to Curtiss-Wright Corporation by General Dynamics C4 Systems and Rockwell Collins, Inc. The contract specifies that Curtiss-Wright provides its General Processor Modules (GPMs) for utilization within the U.S. Army's Future Combat Systems' (FCS') Integrated Computer System (ICS). The ICS synergizes 13 of 14 previously independent platforms within FCS, folding them into one secure, integrated computing environment. The initial order of GPMs is 1,000+ modules, expected to start shipping in Q2 2008.

# Why Design from Scratch?

Get a proven FPGA solution today Reduce your lead time and cost

Customizable FPGA board solutions for interfaces including:

PCI, PCI-X, PCI Express, Gigabit Ethernet, USB, SFP, DDR SDRAM, DDR2 SDRAM, Flash & many more

Available TODAY off-the-shelf, in various FPGA sizes and options

Daughter card customization service available, featuring best-in-class design and a short turn-around time

Long term product availability & support ensures consistent supply and maintenance

Benefit from a low BOM for boards already shipping in volume - discounts for orders of 5 or more pieces

Available for popular Xilinx and Altera platforms

Solutions include FPGA board, IP & software and complete technical and upgrade support from the top-rated supplier of PCIe IP and boards

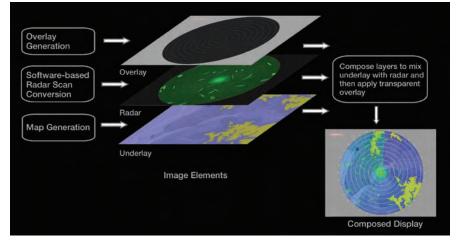

Military command and control displays combine radar video presentation with complex charts and overlay symbology for multi-layer display presentation. Managing the display's layers for timely updates and realistic radar presentation can present difficulties.

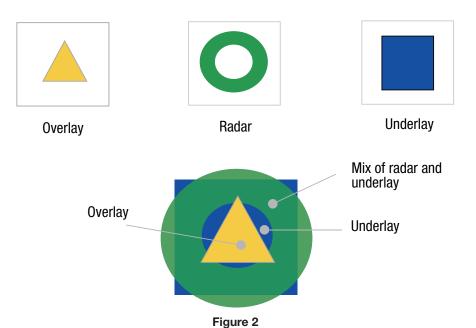

One approach to solving this challenge is to design special-purpose hardware display architectures that support multiple graphics layers. However, developments in COTS processing and Graphics Processor Units (GPUs) have enabled multi-layer displays to be implemented in software without compromising the quality of the display presentation. The new solution allows the compositing of multiple windows of radar video, along with underlay charts and overlay symbology, all updated at different rates and with minimal interaction between the display layers. An example of this is shown in Figure 1, which depicts a combination of underlay, radar, and overlay.

### Standardized hardware platforms

A modern visualization solution for real-time data will employ all-digital processing and display. Sensor data may be supplied directly in digital format - commonplace for modern sensors - or may be converted from its analog legacy interface through a processing server. Standard Ethernet networks provide a cost-effective interconnect from sensors or processing servers through to multiple display clients, possibly incorporating video compression where the number of channels is large or network bandwidth is at a premium.

With the real-time video arriving at multiple display clients, it is highly desirable that the client architecture minimizes the

need for special-purpose hardware such as a radar scan converter. These products have provided an excellent method for radar scan conversion and graphics mixing using innovative techniques, including multi-layer frame stores and video keying. However, if the solution to presenting combined graphics and sensor video could be achieved through software and standard processing and display hardware, the resulting client displays would be more cost-effective, smaller, and flexible. Furthermore, with the inevitable progression in processing and graphics

Figure 1

Furthermore, with the inevitable progression in processing and graphics architectures, software solutions support enhanced and evolving capabilities. In contrast, hardware solutions tend to solve today's problem and offer limited growth or expansion potential.

architectures, software solutions support enhanced and evolving capabilities. In contrast, hardware solutions tend to solve today's problem and offer limited growth or expansion potential.

The need for specialized hardware in clients has tended to limit the capability of a console to reconfigure its role or evolve to new requirements. Often the hardware defines the function, and changes to the function will necessitate changes to the hardware. Furthermore, reduced hardware translates directly to lower maintenance costs and higher system reliability. Where the hardware has industry-standard computing and graphics hardware, the additional cost benefits and ease-of-upgrade serve to further reduce the lifetime cost of deployment.

### Display presentation

The problem of displaying radar sensor video with graphics underlays and overlays is summarized in Figure 1, which shows a logical layering of graphical data with respect to the radar so that some graphics constitute underlay and others the overlay. The distinction of underlay, radar, and overlay in this manner is relevant only in defining the method of presenting the three elements.

The underlay element is likely a complex map composed of many logical layers that build up to form a naval chart. The method of combination requires the radar video to be mixed with the underlay element in a form of cross-mixing, in which pixel color depends on a combination of the graphics color and the radar color. In contrast, graphics drawn in the overlay element will be displayed in preference to any radar or underlay color at that point. It is only if the overlay presents a "transparent" color that the combined radar and underlay show through.

A convenient language and algebra for the description of image combination are provided by Porter and Duff in their seminal work on compositing digital images[1]. They describe the operations for combining images using logical operations, including blending, which they call the over operation. Applying this terminology to the display of radar video, we can define a combination rule that combines an overlay A with radar R and underlay B as:

Display = A over (R over B)

The *over* operator has an associated alpha component, which defines the degree

of transparency in the combination of two pixels. For the R over B operation, the combined radar and underlay graphic is computed from an alpha value that is computed for each display pixel to define the relative weighting between the two elements. This per-pixel alpha value has the requirement to leave the underlay graphics unaffected in the absence of radar, and otherwise display a proportional blend of the radar and graphics color.

The final A over operation demands an alpha value for A of 1 where the pixel is nontransparent and 0 where it is transparent. This implements a color-keyed overlay, where the combination ensures that the radar and underlay only appear when an overlay pixel is transparent. Figure 2 depicts an example where a set of three simple geometric shapes illustrates the combination effects. The combination of the three elements is a real-time process that needs to update the screen to provide smoothly updating graphics and radar video display.

### Finding a software solution

A number of developments in COTS hardware have enabled real-time software compositing to become a reality. First of all, the development of multiprocessor architectures with mainstream multicore

processors provides enormous data processing capability. By designing the software to exploit the multiple processing elements, display-related processing can be allocated to one or more cores with minimal impact on other application processing.

The second development is in modern graphics card performance and architecture. Driven by the seemingly unlimited demands of gaming and simulation, the latest generation of graphics cards provides its own processing capability that serves to offload the main processor and accelerate graphics operations so they run entirely within the GPU's processing and memory subsystem. Significantly, the combination of a multicore processing platform and high-performance graphics subsystem is now an established computing platform available in ruggedized military form. One example is GE Fanuc Intelligent Platforms' MAGIC1 rugged display (see Figure 3).

#### **Practical considerations**

A practical implementation of a softwarebased, real-time image compositor has to do more than provide compositing functions for display elements. It has to work with the constraints of application software, third-party display toolkits, and graphics drivers. In the example shown previously, the underlay map comprises many display layers that may be constructed from a combination of raster and vector components. Such displays are commonly managed by third-party display toolkits, which handle complex display presentation. These toolkits are layered on top of the target computer's native window system, for example, Microsoft Windows or the X Window System for Linux and Solaris.

Application software that employs a toolkit for charting displays needs a radar scan converter and related display processor to present radar video in the layered method described previously. However, the interaction of the radar presentation and the graphical display toolkit needs to be minimal. The desired goal is that the display's graphical component can be managed independently of the radar layer, allowing the low-level graphical libraries to provide the necessary display combinations. Some situations may demand that the radar processing and display functions are handled in a different processing context (in UNIX terms, a process), providing protection against software failures.

### **Exploiting a software framework**

Cambridge Pixel's SPx software framework provides a modern implementation of radar processing, distribution, and display that fully exploits the capabilities of modern processing and display hardware to offer multilayer compositing of real-time data (see case study, next page).

The software provides a capability to render complex, multi-layer graphics applications under both Microsoft Windows and X11 operating systems, supporting true multi-layer displays. The radar layer is updated at regular intervals to provide smooth sweep updates and realistic fading effects. The underlay graphics are mixed with the radar video, and the result is overlaid with another graphics layer containing symbology and track data. The software cleanly separates the radar scan conversion from the display processing, optionally allowing these functions to run on different machines.

An example of the performance achieved can be seen with a complex multi-layer underlay map (an S57 naval chart with 62 thematic layers, 1,400 point features,

Figure 3

4,000 line features, and 1,200 polygons), along with a real-time radar display (500 Hz prf, 4 second scan time). The radar display is updated at regular intervals of 20 ms to provide a highly realistic radar display sweep in 256 levels of radar color. Finally, the map and radar are overlaid with a range ring and target symbology that provides the overlay layer. This complete scenario runs on a rugged desktop computer with a highresolution display of 1,600 x 1,200 x 32 bits per pixel and a Core 2 Duo platform (2.13 GHz processor) with an NVIDIA 7900 graphics card. The typical CPU/GPU load level is less than 10 percent, leaving ample resources for the application software.

SPx software provides flexibility in the display architecture, allowing the scan conversion of the radar video (the conversion from polar to screen) to be handled separately from the display processing, including the option to separate the function across a network. This allows

centralized scan conversion of the radar video and distribution of incremental wedges of new data to the display consoles where the video is composited with the graphics layers. The software is easily reconfigured to move the scan conversion into the display console, distributing the polar video across the network if that configuration is preferred.

### **Industry standard provides** best solution

By eliminating all special-purpose hardware from processing and display functions, industry-standard hardware and software components mean costeffective initial deployment and an openstandards upgrade path for maintenance, repair, and upgrade. A network-based implementation shows radar video distribution from a central acquisition point through a display processor to a number of display consoles. The solution employs only industry-standard computing and display components to present the realtime, multi-layer display.

David Johnson is technical director at Cambridge Pixel. He holds a BSc electronic engineering degree and a PhD in sensor technology from the

University of Hull in the UK. He has worked extensively in image processing, radar display systems, and graphics applications at GEC, Primagraphics, and Curtiss-Wright Controls Embedded Computing. He can be reached at dave@cambridgepixel.com.

> Cambridge Pixel Ltd. **St John's Innovation Centre** +44 (0)1763-260184 www.cambridgepixel.com

#### References:

1. "Compositing Digital Images" T. Porter and T. Duff, Computer Graphics, Vol. 18, No. 3, 1984, 253-259.

## Case study: Naval distribution for Frontier Electronic Systems

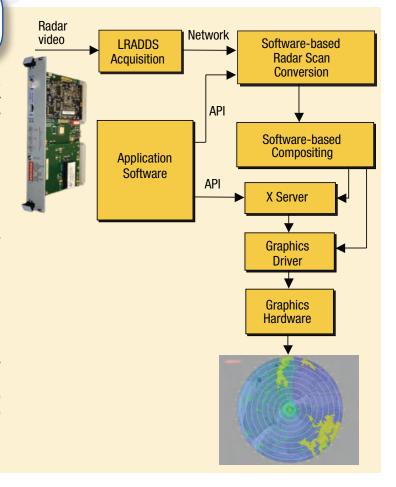

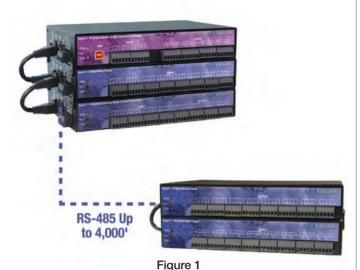

Radar video acquired from a number of sensors onboard a ship can be distributed using a product such as Frontier Electronic Systems (FES) LAN Radar Data Distribution System (LRADDS). Accepting a number of naval formats for radar input, LRADDS provides full bandwidth video on a standard Ethernet network for distribution and processing (see figure).

Cambridge Pixel's SPx radar processor, which uses only industry-standard computing platforms and display components, is capable of accepting LRADDS data and providing clutter processing and display enhancement capabilities before scan converting the data to a PPI display format. The scan conversion can either occur on the display client or, offering the benefits of distributing the processing load, can run on a dedicated radar video server. The server's output is the continually updating radar image, which is distributed to the display consoles for software compositing and display. The console provides a standard X Server for presentation of the underlay and overlay graphic components, with a client application managing the graphics independently of the radar video.

# SATA/IDE SSD

- SATA I, SATA II, IDE and ZIF Interfaces

- 100% compatible with standard hard disk drives

- Form Factors in 1.3"/1.8"/2.5"/3.5"

### Performance

Operating Temp: Industrial and Commercial

Temperature available Access Time: 0.1ms

Power Consumption: 85% less than Average HDD

### Reliability

Shock: 1500G(operating) Vibration: 16G(operating)

MTBF: >1,000,000

### Endurance

Read: unlimited

DuraDrive - Ultra Rugged and Reliable SSDs MasterDrive - Ultra Fast Commercial SSDs

SSD

Now up to 120MB/Sec!

## "AWARD WINNING PRODUCT"

256GB

**DISKCON USA** Best of Show Award

# **Technology:** Imaging — Seeing is believing

# Advanced image processing enables UAVs to fulfil their potential

By Doug Scott

There are many reasons why Unmanned Aerial Vehicles (UAVs) are attracting so much interest - and investment - from military organizations around the world. By not endangering a pilot's life, they can fly missions that would otherwise be judged too dangerous. True autonomy the goal of much UAV research - allows an overall reduction in personnel. And the fact that mission length is potentially not a function of pilot fatigue is highly attractive.

However, mission length - until such time as solar power becomes a viable alternative – is compromised not only by pilot-related factors, but also by the need to refuel. The ideal UAV will never need to return to base for refuelling, and this requirement has been at the heart of substantial research into in-flight refuelling.

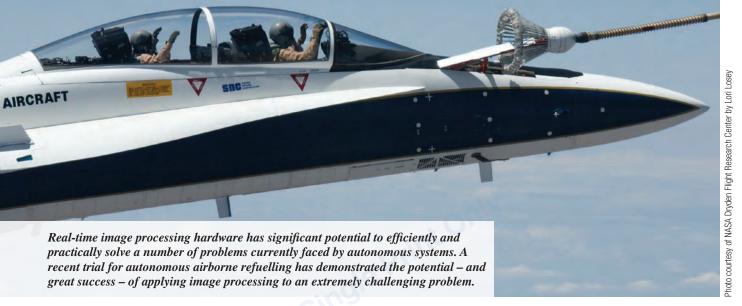

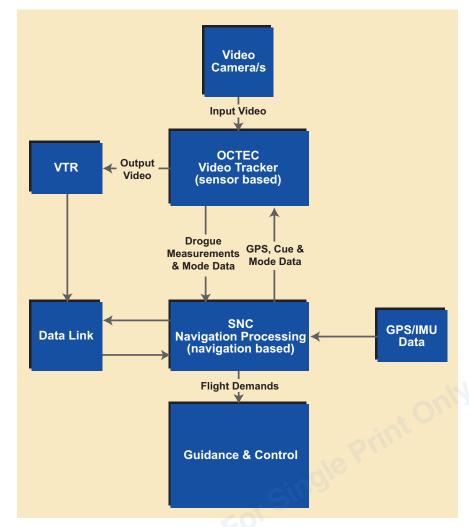

Much development effort has been expended on the potential for GPS technology to enable a refuelling tanker and a receiver UAV to move within close enough proximity of each other to allow docking the fuel probe into the UAV drogue. However, the degree of precision required - especially as either craft is vulnerable to disturbance factors such as turbulence – is at the very outer limits of GPS accuracy. An alternative technology - the use of advanced image tracking and image processing systems - needed to be developed to complement the GPS system to enable a complex, highly sophisticated maneuver (Figure 1).

Evaluating that alternative was the goal of a joint project Advanced Airborne Refueling Demonstration (AARD) developed by the Defense Advanced Research Projects Agency (DARPA) and Sierra Nevada Corporation (SNC). The combined effort produced the first successful demonstration of autonomous probeand-drogue airborne refuelling, and was conducted at NASA Dryden Flight Research Center.

DARPA and SNC settled on using the probe-and-drogue (or hose-and-drogue) refuelling method in the demonstration because it is widely perceived as the most difficult to automate - a function of the flexibility of the hose and its susceptibility to aerodynamic disturbance. Octec - now part of GE Fanuc Intelligent Platforms – and Sierra Nevada Corporation teamed to develop and deliver the image capture and processing functionality that was central to the demonstration's success.

### The challenge

At the project's outset, a number of key studies had to be executed which, in cases such as determining the optimum viewpoint location for the image tracking device and ascertaining the ideal field of view, were interrelated.

Among these studies was an evaluation of alternative image capture approaches. It was known that whichever technology was chosen, the requirement would be to provide a range measurement accuracy of approximately 36 inches at a range of 100 feet to establish the relative positioning of the probe and drogue, closing to an accuracy of 4 inches at a range of 12 feet to allow probe insertion.

Key considerations in selecting the image capture device and the medium used to transmit the captured image data for processing included:

- The resolution of the captured image

- The ruggedness of the device

- Size and weight

- Susceptibility of the transmission medium to the ElectroMagnetic Interference (EMI) that could be expected to be present in an RF-rich environment

Figure 1

It was determined that a high-resolution digital sensor would be the ideal solution; however, its adoption was precluded by any amount of development time necessary to customize the tracker hardware to meet the sensor's digital interface standard. While a high-density fiber optic transmission line was believed to offer the optimum resistance to EMI interference, testing revealed that it gave such a poor image resolution that it was not possible for the tracker to detect a several-pixel object at the extended 30-meter range. The fiber cable also suffered from a relatively large number of dead pixels/fibers.

Finally, a standard NTSC video camera was found to deliver sufficient image resolution to resolve the drogue and basket at a range of 30 meters. A "remotehead" version of the camera was selected to minimize the size and weight impact at the chosen mounting point. The associated transmission cable was shown to offer acceptable resistance to EMI, and the video quality did not indicate any noticeable image interference artifacts.

### **Evaluating alternative** sensor-mounting positions

Although the application is ultimately intended for completely unmanned platforms - both the refuelling tanker and the UAV - the demonstration took place using a manned NASA F-18 flight research aircraft (pictured, first page of article). The four optimum locations for the remote sensor on the F-18 were identified by the NASA flight crew, but modelling and simulation of the desired flight profile and viewpoint constrained the selection to two. The Head Up Display (HUD) view gave close operating range to the drogue and offered the maximum likelihood of the drogue being within the field of view. The view from the inboard right pylon gave good drogue visibility in the terminal phase and had the advantage of being an existing camera position. Both mounting points, however, also had disadvantages that needed to be factored in.

These disadvantages were driven to a large extent by the fact that the tracking algorithm required a minimum of several

pixels on the drogue target for recognition and tracking; this, in conjunction with the NTSC sensor's resolution capability, dictated a maximum Field Of View (FOV) of 55°. Too narrow a point of view would make acquiring the drogue more difficult and would also cause problems as the drogue came closer, filling the entire field of view. Within the event, the optimal field of view was determined to be 55°.

For the demonstration's purposes, two camera positions were used primarily to evaluate their effectiveness. However, deployment of the image-processing hardware within a UAV environment requires only a single camera, minimizing weight and power consumption and avoiding further complexity arising from installing two or more camera sensors at multiple locations on the airframe. This was possible because of the significant development effort in creating algorithms that can accurately estimate range from a single camera.

Provisions were also made in developing algorithms to eliminate background clutter that could be mistakenly identified in the captured image. For example, some of the aircraft structures such as the engine exhaust nozzles and fuel hose exit aperture, under certain lighting conditions, appear very much like the drogue at extended distances. Areas behind the tanker that should be avoided – described as "avoidance volumes" – were determined through simulation.

Another challenge in accurately identifying the position and distance of the drogue relative to the hose resulted from trial video analysis. This showed that the instability of the drogue's outer rim (Figure 2) made it an inappropriate reference point. However, the drogue's solid inner hub was found to exhibit stable high contrast, making it relatively easy for the sensor to identify and providing a practical calibrated reference point.

Figure 2

# Measuring range from a single camera

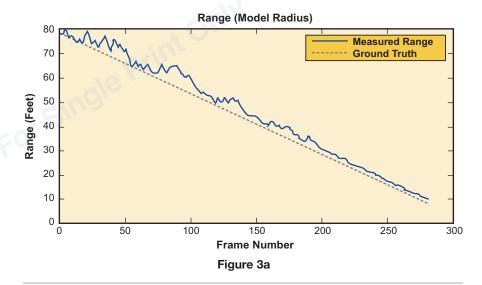

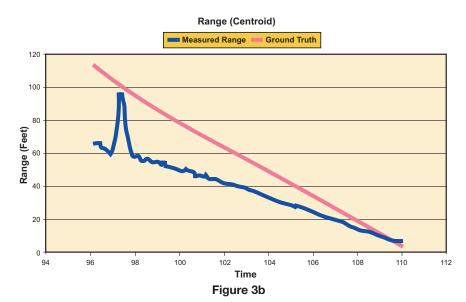

A significant effort was expended to develop the appropriate range estimation algorithms, and two were proposed. One was based on a classical centroid approach; the other was a model-based approach. The algorithms were implemented in MATLAB and tested against the simulated models.

It was determined that each algorithm has complementary strengths and weaknesses. The centroid-based approach delivered superior resolution due to its measuring an area in image pixels, while the model-based approach was more stable and more accurate by comparing the observed video pattern with a known reference.

Figures 3a and 3b show the reported estimates from each algorithm against a known true range for each image field in the video sequence. As expected, the model-based approach is noisier at the further ranges than the centroid-based approach; however, the centroid-based algorithm suffers from gain and offset bias in its ability to measure accurately.

The decision was made to implement both algorithms running in parallel. This resulted in a measurement accuracy better than 10 centimeters from a range of approximately 3 meters. Desired accuracy was originally specified as 1-sigma (that is, 68 percent of the time) standard deviation; the accuracy achieved was predominantly better (that is, it was within the given range about 90 percent of the time – almost 2-sigma standard deviation).

As expected, the model-based approach is noisier at the further ranges than the centroidbased approach; however, the centroid-based algorithm suffers from gain and offset bias in its ability to measure accurately.

At the heart of the automated airborne refuelling demonstration was Octec's ADEPT-60 sensor-based video tracking and image processing module (Figure 4). It is natively equipped with several image processing algorithms and extended to enable the measurements from the newly developed algorithms to be combined. This provided the flexibility to optionally estimate the range without direct interaction between the underlying algorithms.

The increasing proportion of the field of view occupied by the drogue as it moved closer to the refuelling tanker - from a few pixels at a distance of 30 meters to more than half the field of view during the docking phase – led to the requirement to modify the tracking algorithm to contain a resizable image template of the target in memory, which is dynamically updated using the estimated drogue size. The template image also served as a first-stage mechanism for reacquiring the drogue in the event of an intermittent track loss.

Figure 4

As noted earlier, the selected mounting points for the image sensors were not without their drawbacks. Most significant among these was a concern that the HUD cockpit window would induce significant image distortion. This issue was addressed by calibrating the system using "real world" measurements of various 3D points around the aircraft and hangar, and tracking these same points through the image capture sensor. An optimization routine was written in MATLAB to model the camera and lens parameters, and the known 3D points were reprojected through the model and compared with those measured by the vision system. This allowed the processing algorithms to be modified to compensate for anomalies in the camera's field of view.

### The next phase

The demonstration proved that the application of advanced vision-based sensors for image capture and state-of-the-art image processing technology to augment the existing capabilities of sophisticated GPS-based positioning systems can be achieved. However, work to maximize the viability and deployability of this technology continues. Overall performance in acquiring the target image can be increased. Operating range – the initial distance at which the drogue can be captured - can also be extended, reducing the reliance on very precise GPS-based measurements. Finally, work will be done to enable drogue type identification, recognition of anomalous drogue behavior, and the effects of lighting and weather conditions.

Doug Scott is an algorithms development engineer at Octec Ltd., part of GE Fanuc Intelligent Platforms. He joined Octec in 2001 to develop

various algorithms for automatic video trackers and image processing hardware. He holds a BSc Eng. in Electronics from the University of the Witwatersrand, South Africa. He can be reached at doug.scott@gefanuc.com.

**GE Fanuc Intelligent Platforms** +44 (0)1344-465200 www.gefanucembedded.com

# **NEW Standard** for stackable **PCI Express bus!**

MSM945P | SMX945 | PCI/104-Express Peripherals

### MSM945P incl. SMX945

- PCI/104-Express Baseboard

- Intel® Core™ 2 Duo L7400 DDR2-RAM 256 - 2048MB

- Core™ Duo 2x 1.6GHz

- 6x USB V2.0, 2x SATA, 1x DIE

- LAN Ethernet 10/100BASE-T

- COM1-2, LPT1

- Ext. Temp. -40°C to + 70°C

### New PCI/104-Express Peripherals:

- MSMGE104EX: 1x 1GB-LAN

- MSM4E104EX: 4x 1 GB-LAN

- MSMSA104EX: 2x SATA300

- MSMG104EX: 4x Framegrabber, 16 channel Videoinput

- MSMEC104EX: ExpressCard 34/54

- MSMMX104EX: PEG x16 Graphic with ATI E2400

DIGITAL-LOGIC AG offers reliable **Embedded Computers** in PCI/104e, 3.5", EPIC, EBX, smartModule, **COM Express** and other formats.

Further information:

www.digitallogic.com

**Technology:** Imaging — Seeing is believing

Remote Monitoring Debriefing System (RMDS) conceived and developed by the Israel Aircraft Industry (IAI)

By Yehuda Singer, PhD

The Remote Monitoring Debriefing System (RMDS) is intended for the first solo flights of a pilot trainee. It enables the trainer to monitor the flight in real time and to play back the flight later to provide detailed feedback and instructions. The system performs: 1) flight planning; 2) real-time flight monitoring; and 3) post-flight processing and comparison of the intended flight plan to the performed flight simulation.

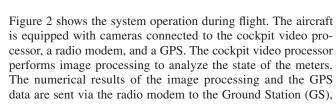

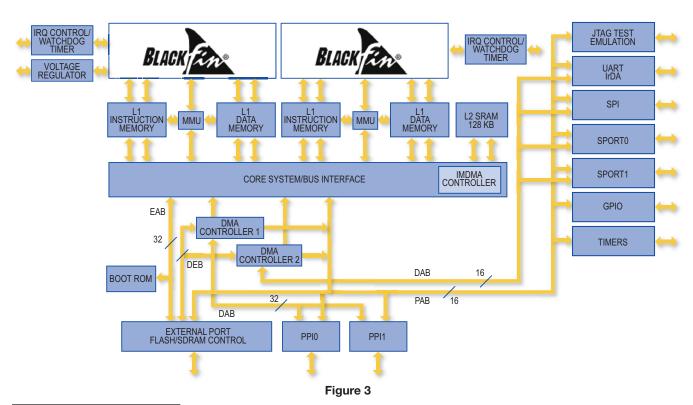

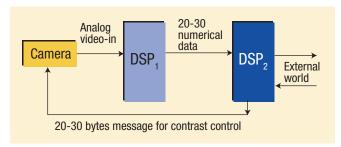

Yehuda focuses on real-time flight monitoring and shows the system analysis process that led IAI & Beyond2000 to choose a dual core DSP architecture based on Analog Devices' BF561.

A pilot trainee performing his or her first solo flights could commit errors that could lead to serious accidents. A simple solution is to put a video camera in the cockpit and transmit real-time video to the trainer monitoring the flight from the ground. However, the transmission of a digital video at the rate of 15 frames per second necessitates bandwidth of 160 Mbps. The cost of such a channel is prohibitively expensive. The question is how to avoid transmitting video and still monitor the state of the aircraft in flight. The solution is to perform image processing on the input video and transmit numerical results to the ground. Transmitting numerical results requires a bandwidth of only 9,600 bits per second, which is easily and economically transmitted over an RF radio modem (see Figure 1).

Figure 1

Figure 2

which restores the view of the panel and the 3D map as closely as possible to the real view seen in the aircraft. The platform of the GS is based on the FSX-Microsoft Flight Simulator.

To achieve a ground that is as close as possible to real video, we need to perform image processing at the rate of 15 frames per second on each camera.

### System analysis

At the system analysis stage of the project, the computer requirements are:

- 1. CPU load is 30 percent

- 2. The bandwidth of the memory and bus is 40 percent

The assumptions for estimating the usage of these resources are:

- 1. The image processing is performed on a set of Regions Of Interest (ROIs)

- 2. Each ROI is  $100 \times 100 \text{ pixels} = 10^4 \text{ pixels}$

- 3. There are 20 ROIs

- 4. 15 frames per second

- 5. Memory access of 10 ns, which relates to failure in accessing the cache memory.

- 6. A CPU faster than the memory is delayed by the memory whenever it accesses it.

Therefore, to estimate the CPU load, we have to count the number of memory accesses in our algorithm. Since the algorithm does not access the memory sequentially, we take a larger value of the memory access time. Table 1 shows the CPU load, which is much higher than desired: more than 54 percent compared with the value of 30 percent corresponding to the typical requirements. Table 2 shows the required memory bandwidth. It is a little more than 40 percent.

| Function       | Memory accesses               | CPU load in 1 second |

|----------------|-------------------------------|----------------------|

| Threshold      | 2 x 15 x 20 x 10 <sup>4</sup> | 0.06                 |

| Contrast       | 2 x 15 x 20 x 10 <sup>4</sup> | 0.06                 |

| Vibration      | 10 x 15 x 20 x 10⁴            | 0.3                  |

| Identification | 4 x 15 x 20 x 10 <sup>4</sup> | 0.12                 |

| Total          | 18 x 15 x 20 x 10⁴            | 0.54                 |

Table 1

| Function                            | MBps  |

|-------------------------------------|-------|

| Video in (2 x 15 frames, 525 x 858) | 25.76 |

| Video out                           | 12.88 |

| Internal memory transfer            | 2.86  |

| Total                               | 41.5  |

Table 2

In the next section we shall introduce other considerations in choosing the computation platform for our project.

### Choosing a platform

Software development associated within such a project is the critical path; hence, the requirement was to find an off-the-shelf evaluation board with two processors and start the software development without any wait for hardware development. At the end of 2004, we chose the Analog Devices BF561 dual-core as a platform for our project. By choosing the BF561 (see Figure 3), we removed the bottleneck of CPU time.

Memory bandwidth is supported by:

- 1. A separate cache for instruction

- 2. A separate cache for data

- 3. A fast DMA to capture streaming video in and out.<sup>1</sup> (In addition, the BF561 has standard I/O resources such as RS-232, SPI, and parallel I/O)

<sup>&</sup>lt;sup>1</sup>Video out is needed for debugging purposes.

Analog Devices' evaluation board, the ADSP-BF561 EZ-KIT Lite,<sup>2</sup> enabled us to start software development immediately. I/O not included on the evaluation board was implemented on an extension board connected to the evaluation board via backward connectors.

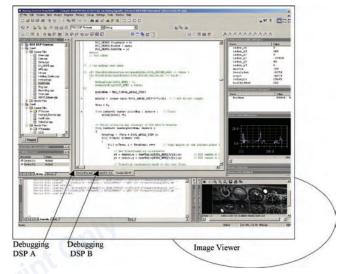

The software tools associated with the BF561 permit one PC to serve as a development platform controlling the two DSPs (see Figure 4). Of course the software development process of a multiprocessor becomes simpler when the development system is controlled by one PC. In addition, software development of a realtime image processing application implies supporting utilities to the Integrated Development Environment (IDE). It is necessary to display the input image as sampled by the video decoder in the DSP. Figure 5 shows an image captured by the video decoder and stored in the DSP's memory. The image is displayed by the image viewer, which is a part of the IDE. This feature helped in integrating progressive scan video cameras. The progressive video is essential in image processing applications in a vibrating environment. The camera produces a TV standard that is 525 lines and 858 columns. The image produced by the camera is at the size of 640 x 492 pixels per frame. The image viewer helped in finding the input video's real size, which is 525 x 858.

### Software design to enhance performance

The two cores interact via a shared memory. The shared memory is an external DRAM controlled by external port flash/SDRAM (see again Figure 3). The utilization of the two cores depends on the functional decomposition of the project. In an ideal situation when the computation task can be decomposed into independent subtasks, the processors are fully utilized. On the other hand, if the functional decomposition yields interdependent subtasks, much time is spent on synchronizing the processors in accessing the data in the shared memory. The design goal

Figure 4

<sup>2</sup>We used the evaluation board as a part of the first prototypes delivered to the first customers and for the experimental flights.

is to minimize these interdependencies; hence, the processors become loosely coupled.

Figure 5 shows the functional decomposition of our system. Each DSP has its own cache memory instruction and cache memory data. One DSP samples the video from the camera and performs image processing only, while the second DSP interfaces the external world:

- 1. To the GS via the RF modem

- 2. To the GPS

- 3. To the contrast control of the cameras

Figure 5

The DSP performing the image processing handles the second DSP with numerical results and the contrast values via the shared memory. The second DSP does not acknowledge the acceptance of these data, reducing our synchronization costs.

This functional allocation of tasks to the two DSPs guarantees that they are loosely coupled; thus, their computational power is maximized.

### Video processing

The streaming analog video is captured by the video decoder, which converts it to digital and transfers the converted video to the external memory by one of the DMA channels. When a frame is completed:

- An interrupt is generated to the DSP when a new frame has been received and is stored in memory.

- DMA switches automatically to get an additional frame in a new memory buffer without the interference of the DSP.

The DSP processes the frames concurrently while new frames are captured by the video decoder. To enhance performance, portions of the images that relate to the ROIs are transferred from the DSP's external memory to its internal memory.

To enable debugging in real time, we produce an image with video markers on a monitor TV that shows the last frame processed. However, our input video is a progressive scan type, while a monitor TV supports interlaced video.

Figure 6 lists line information on the two types of video. A progressive scan video frame is composed of a contiguous sequence of 525 lines starting at line 0 and ending at line 524. An interlaced video is composed of two subframes: One subframe is a sequence of all even lines starting at line 0 and ending at line 524; the other subframe is a sequence of all odd lines starting at line 1 and ending at line 523. We again used the fast DMA that is part of the BF561 to convert the progressive video to an interlaced video. In addition, we added special markers to show the results in video for debugging and recording for debug purposes.

| Progressive Video   | Interlaced Video    |

|---------------------|---------------------|

| Line <sub>0</sub>   | Line <sub>o</sub>   |

| Line,               | Line <sub>2</sub>   |

| Line <sub>2</sub>   | Line₄               |

|                     |                     |

|                     |                     |